SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

About Synaptic Laboratories Ltd (SLL) – xSPI MEMORY IP SPECIALISTS

Since 2016 SLL focusses almost entirely on the development and support of IP for all xSPI memories. {x8 / x16 PSRAM, x8 NOR Flash, Multi-Chip Packages and STT-MRAM}

Manufactured by 8 or more memory companies. Sold into many high volume ASIC markets for many years. SLL IP’s enable their use in many FPGA families.

Focussed specialised knowledge. Rapid expert support. Close relationships with all manufacturers. Extensive experience in a very wide range of xSPI projects and applications since 2016. This sets SLL apart from every other xSPI IP provider.

SLL IP is trusted in very high value projects. Reduces risks and costs and helps project success. The right expert guidance at the right time can save your company far more than the very economical price of our IP licenses.

Sensors, industrial control and automation, medical and dental, transport, photonics and communications, video and radar and other imaging, lighting, electricity generation and testing, aerospace mission systems, etc, etc.

Fast chip to chip communications (e.g. MCU to FPGA). A widely used Multiple Bus memory controller. Why and how to replace your slow configuration flash.

All ~ 8 xSPI memory manufacturers, and all related protocols {HyperBus, OctaBus, Octal Bus, …}, and most major FPGA families.

NEWS: SLL SUPPORTS CRITICAL LINK’S EXCITING NEW MITYSOM WITH xSPI MEMORY

SLL is pleased to announce appointment as the EXCLUSIVE SUPPLIER of xSPI memory controller IP to Critical Link for their exciting new MitySOM C10L Dev Kit and SOM. This hardware has an Intel C10LP FPGA and xSPI memory. The MitySOM Dev Kit is a low cost replacement for the discontinued Intel C10LP Eval Kit.

NEWS: SLL SUPPORTS EVERSPIN’S STT-MRAM – THE WORLD’S FASTEST NON-VOLATILE xSPI MEMORY

SLL is OFFICIAL SUPPLIER of xSPI memory controller IP to EVERSPIN for their fast and exciting STT-MRAM EMxxLX xSPI Family of Products.

NEWS: SLL IS NOW OFFICIAL SUPPLIER OF xSPI MEMORY CONTROLLER IP TO:

Microchip for PolarFire SoC and FPGA’s.

Intel for the Cyclone 10 LP Eval Kit.

– Also supporting most Intel FPGA devices

Critical Link for the MitySOM C10L Eval Kit and SOM.

Lattice – Watch this space!

We also partner with TRENZ Electronics for their development boards and SOM.

XILINX: SLL IP also supports all Xilinx devices including UltraScale and UltraScale+.

We are trusted

Some examples of our customers:

Microchip

Lattice Semi

Collins Aerospace

Hamamatsu Photonics

L3Harris

Elbit Systems

GC Dental

Caterpillar's Progress Rail

Qualcomm

Basler

TRIUMF

Singapore Agency SIMTech

Bonfiglioli

Progeny

SICK AG

Advanced Research Associates

xSPI FPGA Configuration

with Fast Re-Use

Product code: Boot with Fast Re-use

Replace your slow SPI or QSPI flash with a faster or better FPGA fabric configuration device.

This solution employs SLL’s xSPI Multiple Bus Memory Controller (xSPI MBMC).

xSPI MBMC allows you to select from a wide range of low pin count, faster, or better, configuration devices:

- 200 MHz DDR x8 xSPI NOR Flash devices from

Infineon, ISSI, Gigadevice, Macronix and Micron - Exciting 200 MHz DDR x8 STT-MRAM from Everspin

(Nonvolatile memory with PSRAM like performance) - 200 MHz DDR x8 Multi-Chip Packages

(NOR Flash and PSRAM on the same ~12 I/O pins)

This exciting solution will deliver:

- Far superior memory bandwidth after FPGA fabric configuration

- Potential to reduce the number of devices and board area in your design

Easy to evaluate on COTS development boards from SLL hardware partners with SLL trial IP.

xSPI Multiple Bus Memory Controller

The industry 'defacto standard' memory controller for xSPI-like memories

Product code: xSPI MBMC

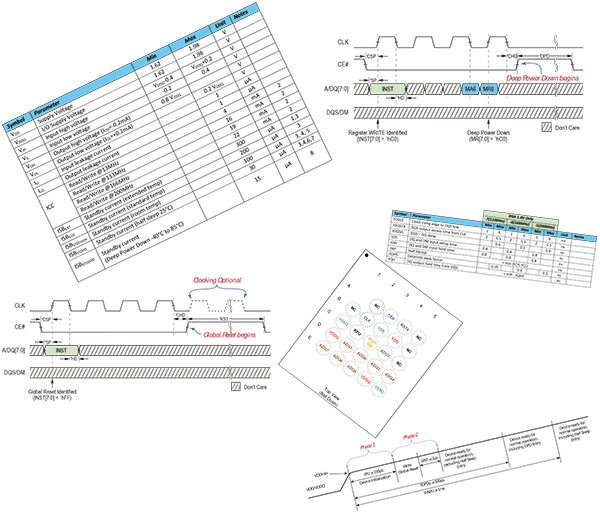

One very small memory controller for FPGA and ASIC that supports:

- NOR Flash, PSRAM (with ECC), exciting xSPI STT-MRAM

- JEDEC xSPI Profile 1.0 & 2.0

- HyperBus 1.0, 2.0 & 3.0

- OctaBus, Octal Bus

- Xccela Bus

- All the 9 memory vendors making these devices

- Up to 250 MHz DDR, with x4, x8 and x16 data paths

- HyperBus and Octal Bus 200 MHz DDR x8 Multi-Chip Packages (MCP)(NOR Flash and PSRAM on the same ~12 I/O pins)

- Multiple package sizes, from tiny WLSCP, 4mm x 4mm BGA49, 6mm x8mm BGA24, 8mm x 8mm BGA24, 6mm x 8mm BGA 24 MCP and 8mm x 8mm BGA 24 MCP

- Support for many FPGA device families

- Low cost COTS evaluation boards are available with SLL trial IP

Fast Chip To Chip Communications

Product code: Chip to Chip Communications

Fast and efficient bidirectional chip to chip communications

over Octa, Octal and xSPI Profile 2.0 PSRAM protocols

⚡ High bandwidth

⚡ Low latency

Tightly coupled BIDIRECTIONAL communications between:

- Your chosen ASIC microcontroller unit (MCU) ↔︎ your chosen FPGA

- Your chosen ASIC microprocessor unit (MPU) ↔︎ your chosen FPGA

- Your chosen FPGA’s: FPGA ↔︎ FPGA

Suitable for use with all MCU that have HyperBus compatible memory controllers.

Memory Management and

Memory Protection Solutions

Product code: eMMU eMPU

Significant advances for MMU’s and MPU’s in embedded applications:

- Tiny footprint solution for very resource constrained designs

- Exceptional real-time memory management capabilities for processors and peripherals

- Patents awarded USA, South Korea, …

One example:

- The best features and capabilities of both a memory protection unit (MPU) and

a memory management unit (MMU) in one tiny module.

Breakthrough Safe and Secure

Real Time Architecture

Product code: SSRT

Multi-core and many-core SSRT features:

- support for all real-time operating systems

- processor agnostic

- statically time analyzable

- improves use of all alternate timing analysis approaches

- simplifies writing real-time software

- higher performance

- and more (patents awarded)

SLL Customers

SLL commercial customers include Fortune Global 500’s, government agencies, scientific organizations and institutes, and

SME’s from North America, across the EU and EFTA countries, and to Japan and China.

SLL also works with third party design houses that are working as subcontractors on commercial and government contracts

SLL also works with the FAE of SLL partner companies and with the FAE of their electronics distribution companies (Arrow, Digi-Key, Macnica and others) in all regions and with their end customers.

SLL IP's Applications

SLL IP’s are employed commercially in many applications.

Some examples include:

- Industrial control systems

- Industrial automation systems

- Medical products

- Dental products

- Transport (trains and helicopters)

- Aerospace mission management systems

- Industrial lighting

- Electricity generation and distribution testing equipment

- Photonics and communication systems

- Video systems

- Radar and other imaging and sensor products and systems

- Scientific measuring and testing equipment

- COTS FPGA development boards as bundled IP

- Others

Customers can easily use SLL solutions on COTS and proprietary development boards. All major FPGA vendors' devices are supported:

Trial and Reference Designs

SLL provides trials with reference designs for several of our IP’s.

SLL reference designs have been downloaded thousands of times.

SLL is the expert intermediary between our customers and partners

About Synaptic Laboratories Ltd (SLL)

COTS semiconductor IP (SIP) for many embedded applications in FPGA and ASIC hardware. ⭐ Patents awarded in many countries

Leading FPGA and memory vendors choose SLL to be their semiconductor IP provider partner

Fortune Global 500’s, SME’s, research institutions… globally

SLL supports our partners’ FAE and electronics distribution companies FAE in all regions

⚡ IP design house ⚡ Project design guidance ⚡ FPGA design shrink and optimization ⭐ Excellent customer support