SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

Navigating the Memory Maze: How the SLL xSPI Multiple Bus Memory Controller is Streamlining Embedded Systems

As needs and technologies evolve in the world of embedded systems, memory remains a critical cornerstone.

Its selection and efficient integration directly impact performance, power consumption, and the overall cost-effectiveness of a design. Choosing the right memory type, capacity, and interface is a complex balancing act. As demands for higher bandwidth and lower power continue to grow, traditional memory interfaces struggle to keep pace. This is where the emergence of xSPI-like memories and sophisticated controllers like the Synaptic Laboratories Ltd (SLL) xSPI Multiple Bus Memory Controller (MBMC) are revolutionizing the landscape.

This blog post delves into the importance of memory in embedded systems, explores the advantages of xSPI-like memories, and highlights the features and benefits that make the SLL xSPI MBMC a leading solution for interfacing with these advanced memories in both FPGA and ASIC environments.

The Vital Role of Memory in Embedded Systems

Embedded systems are ubiquitous, powering everything from smartwatches and IoT devices to complex industrial machinery and automotive control units. Regardless of the application, memory plays a fundamental role by providing:

- Storage for Code: The embedded system’s firmware, operating system, and application software reside in memory. The performance of code execution is directly tied to the memory’s access speed and bandwidth.

- Data Storage: Embedded systems often handle and process vast amounts of data, requiring ample memory to store sensor readings, configuration parameters, and temporary results.

- Buffering and Caching: Memory acts as a buffer to smooth out data flow between different system components, mitigating latency and improving overall responsiveness. Caching techniques leverage faster memory regions to store frequently accessed data, further boosting performance.

- Real-Time Operations: Many embedded systems operate in real-time, requiring deterministic and predictable memory access times. The choice of memory and its interface significantly affects the system’s ability to meet these strict timing constraints.

Therefore, the selection of memory is not a trivial task. It necessitates careful consideration of several factors, including:

- Density: The amount of storage capacity required.

- Speed: The access time and data transfer rate (bandwidth).

- Power Consumption: Crucial for battery-powered and energy-sensitive applications.

- Cost: Balancing performance with budgetary constraints.

- Interface: The protocol used to communicate with the memory.

- Reliability and Endurance: The lifespan and data retention characteristics.

- Physical Size and Packaging: Important for space-constrained designs.

Limitations of Traditional Memory Interfaces

Traditional memory interfaces, such as parallel NOR and NAND flash, have served embedded systems well for many years. However, they face increasing limitations in meeting the demands of modern applications. Some of the key drawbacks include:

- Low Bandwidth: Parallel interfaces require a large number of pins, increasing board complexity and cost. Even with wider data buses, achieving high bandwidth can be challenging due to signal integrity issues and timing constraints.

- High Power Consumption: The parallel nature of these interfaces necessitates driving a large number of signals simultaneously, resulting in significant power consumption.

- Large Footprint: The increased pin count translates to larger packages and larger board footprints, which is detrimental in space-constrained applications.

- Complexity: Designing and implementing controllers for parallel memory interfaces can be complex, requiring specialized expertise and significant development effort.

Enter xSPI-like Memories: A New Paradigm

xSPI (eXpanded Serial Peripheral Interface) and similar serial protocols are emerging as a compelling alternative to overcome the limitations of traditional parallel interfaces. These protocols offer several advantages:

- High Bandwidth: xSPI protocols can achieve significantly higher bandwidth compared to parallel interfaces by utilizing a smaller number of pins and operating at higher clock frequencies. Techniques like Double Data Rate (DDR) further enhance bandwidth.

- Low Power Consumption: The reduced pin count and serial nature of xSPI minimize power consumption, making it ideal for battery-powered and energy-sensitive applications.

- Small Footprint: The fewer pins result in smaller packages and reduced board footprint, enabling more compact designs.

- Simplified Interface: While the underlying protocol might be complex, dedicated xSPI controllers abstract away much of the complexity, simplifying the integration process.

xSPI is not a single, rigidly defined standard. Instead, it refers to a family of serial protocols that share similar characteristics and objectives. These protocols often feature:

- Single-Ended Signaling: Reducing cost and complexity compared to differential signaling.

- Command/Address/Data Phase Separation: Streamlining the communication process.

- Standardized Command Set: Facilitating interoperability between different vendors.

- Scalable Bandwidth: Allowing for different operating modes and data bus widths (e.g., single, dual, quad, or octal) to adapt to different performance requirements.

Examples of xSPI-like memories include Octal SPI (OSPI) and HyperFlash, which are becoming increasingly popular in automotive, industrial, and consumer electronics applications.

The Synaptic Laboratories Ltd (SLL) xSPI MBMC: Your Gateway to Efficient Memory Integration

Interfacing with xSPI-like memories requires a dedicated controller that can handle the complexities of the protocol and provide a seamless interface to the host system. This is where the Synaptic Laboratories Ltd (SLL) xSPI Multiple Bus Memory Controller (MBMC) shines.

The SLL xSPI MBMC is a high-performance, configurable IP core designed to simplify the integration of xSPI-like memories in both FPGA and ASIC environments. It offers a wide range of features and benefits that make it a compelling choice for embedded system designers:

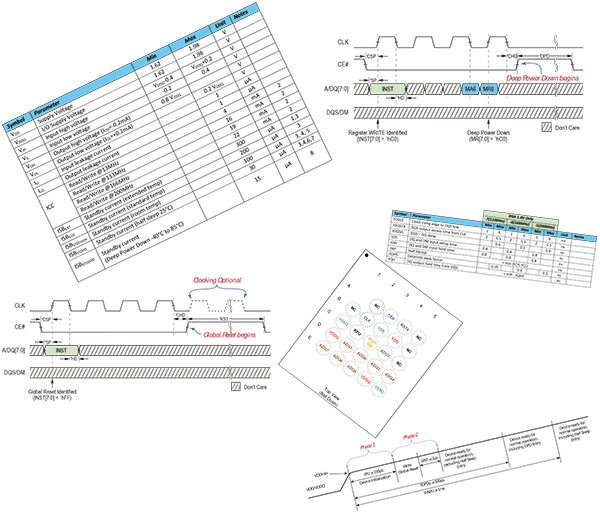

- Comprehensive xSPI Support: The MBMC supports a wide range of xSPI-like protocols, including OSPI, HyperFlash, and other similar interfaces. This provides flexibility and future-proofing, allowing designers to choose the most appropriate memory for their application without being locked into a specific vendor or protocol.

- High Performance: The MBMC is optimized for high bandwidth and low latency, enabling the embedded system to achieve its full performance potential. It supports various operating modes, including DDR and octal data bus widths, to maximize data transfer rates.

- Configurability: The MBMC is highly configurable, allowing designers to tailor the controller to their specific needs. This includes configurable address spaces, command sets, timing parameters, and error handling mechanisms.

- Multiple Bus Support: The “Multiple Bus” aspect of the name highlights a key feature: the MBMC can manage multiple xSPI memory devices simultaneously. This is crucial for applications requiring large memory capacities or parallel data access. The ability to interleave data across multiple memory devices significantly increases overall bandwidth.

- AHB/AXI Interface: The MBMC provides a standard AHB (Advanced High-performance Bus) or AXI (Advanced eXtensible Interface) interface to the host system, simplifying integration into existing system-on-chip (SoC) architectures. These industry-standard interfaces ensure compatibility and ease of use.

- Direct Memory Access (DMA) Support: The MBMC can be configured to support DMA, allowing data to be transferred between the memory and other system components without CPU intervention. This offloads the CPU and improves overall system performance.

- Error Detection and Correction (ECC): The MBMC can be configured to support ECC, providing robust data protection and ensuring data integrity. This is particularly important in mission-critical applications where data corruption can have serious consequences.

- Power Management Features: The MBMC incorporates various power management features, such as clock gating and power gating, to minimize power consumption. This is crucial for battery-powered and energy-sensitive applications.

- FPGA and ASIC Implementation: The MBMC is available as both a soft IP core for FPGA implementation and a hard IP core for ASIC implementation. This provides flexibility and allows designers to choose the most appropriate implementation technology for their application.

- Comprehensive Documentation and Support: Synaptic Laboratories Ltd provides comprehensive documentation and support for the MBMC, making it easy for designers to integrate and use the controller effectively.

Benefits of Using the SLL xSPI MBMC

Choosing the SLL xSPI MBMC offers several significant benefits:

- Reduced Development Time: The MBMC simplifies the integration of xSPI-like memories, reducing development time and effort. Designers can focus on their core application logic rather than spending time developing and debugging complex memory controllers.

- Improved Performance: The MBMC’s high-performance architecture and configurable features enable the embedded system to achieve its full performance potential.

- Lower Power Consumption: The MBMC’s power management features minimize power consumption, extending battery life and reducing energy costs.

- Reduced System Cost: The MBMC’s simplified interface and efficient design can help to reduce system cost by minimizing the number of components required and reducing board complexity.

- Increased Reliability: The MBMC’s ECC support and robust design ensure data integrity and increase system reliability.

- Future-Proof Design: The MBMC’s support for a wide range of xSPI-like protocols provides flexibility and future-proofing, allowing designers to easily adapt to new memory technologies as they emerge.

Conclusion: Embracing the Future of Embedded Memory Interfaces

The increasing demands of modern embedded systems necessitate the adoption of advanced memory technologies and efficient interface solutions. xSPI-like memories are emerging as a powerful alternative to traditional parallel interfaces, offering significant advantages in terms of bandwidth, power consumption, and footprint.

The Synaptic Laboratories Ltd (SLL) xSPI Multiple Bus Memory Controller (MBMC) is a leading solution for interfacing with these advanced memories, providing a comprehensive set of features and benefits that simplify integration, improve performance, and reduce system cost. By embracing the MBMC, embedded system designers can unlock the full potential of xSPI-like memories and create more powerful, efficient, and reliable embedded systems. As xSPI adoption continues to grow, the SLL xSPI MBMC is poised to become the de facto standard for interfacing with these memories in both FPGA and ASIC environments, paving the way for the next generation of embedded devices.

SLL is the only specialist, dedicated xSPI SIP design house since 2016. XSPI SIP design and support is SLL core business, for FPGA and ASIC. Visit our website to learn about SLL’s highly innovative xSPI SIP portfolio that is already successfully used by global customers including Fortune Global 500’s, and in 100m+ volume ASIC projects.

Subscribe to our Newsletter

Lorem ipsum dolor sit amet, consectetur adipiscing elit. Ut elit tellus, luctus nec ullamcorper mattis, pulvinar dapibus leo.