SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

FPGA (SoC) configuration using 200 MHz DDR x8 NOR Flash

LATEST NEWS

Get more from your FPGA and SOC configuration flash!

FPGA (SoC) configuration using 200 MHz DDR x8 NOR Flash overview

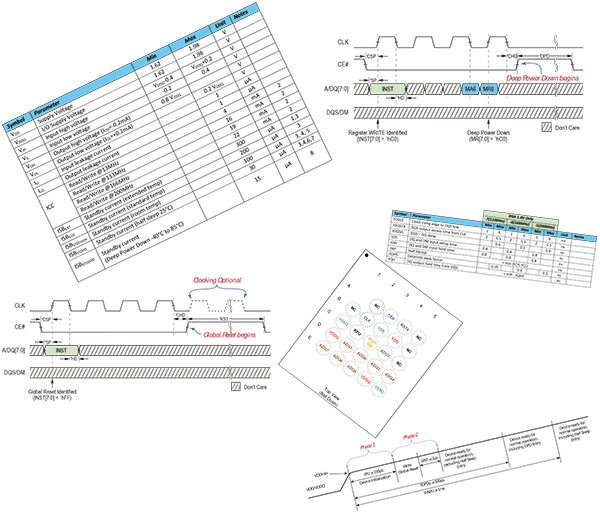

The newest addition to SLL’s IP portfolio allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, 200 MHz DDR x8 NOR Flash from Infineon, ISSI, Gigadevice, Macronix, Micron or a 200 MHz DDR x8 STT-MRAM device from Everspin.

SLL is GigaDevice’s partner

Micron Technology, Inc

SLL collaborates closely with Micron

SLL collaborates closely with Macronix

SLL is an Infineon Associated Partner

Why use SLL’s solution:

- Today’s FPGA and SOC device families use slow NOR Flash configuration devices.

- These legacy NOR Flash devices have slow performance when accessed from within the FPGA fabric, pushing developers to copy executable code and other performance sensitive data from legacy NOR Flash to external volatile memories such as DDRx SDRAM.

- SLL’s solution allows you to increase system performance, reduce pin count, and reduce bill of materials.

What stays the same:

- Your design will still power-on in legacy SPI or QSPI mode, to configure the FPGA at full SPI or QSPI performance.

- So this solution is suitable for PCIe and other fast-boot applications that require full QSPI performance.

- Advantageously, you will continue to use Intel’s Quartus Programmer to load the FPGA bitstream images over JTAG.

The SLL difference:

- SLL IP instantiated in the FPGA fabric enables access to the x8 configuration NOR Flash device in high throughput 8D-8D-8D mode, for far superior run-time performance after boot.

Benefits:

- Exactly the same FPGA power on configuration time as when using legacy NOR Flash.

- Much much faster system performance after power on, due to the ability to access the external configuration memory device in double data rate (DDR) x8 mode (8D-8D-8D).

- Reduced time to first response from the soft core processor in the FPGA, due to the ability to directly execute code from NOR Flash at high speed.

- The ability to add a x8 PSRAM device on the same (low count) I/O memory pins as the xSPI NOR flash. So your designs can have both NOR Flash and PSRAM, accessed with high performance, without increasing the use of I/O pins.

- Also, multiple chip packages that combine octal NOR Flash with octal PSRAM in the same 8mm x 8mm BGA24 package can be used to provide low board area solutions

- It can reduce your BoM through potentially less memories in your design, less board area, and increased run-time system performance with lower pin-count.

Which FPGA device families are supported:

- Intel Cyclone 10 LP, Cyclone IV

- Intel Cyclone V, Cyclone 10 GX, Arria V, Arria 10, Stratix V.

- Please contact us regarding AMD-Xilinx 7-Series support.

Which xSPI memory device families are supported:

- Infineon Semper Flash with HyperBus Interface

- ISSI Octal Flash

- Gigadevice Xccela Flash

- Macronix OctaFlash

- Micron Xccela Flash

- Everspin STT-MRAM

SLL’s solution is already being adopted by industrial customers in Germany. SLL is ready to work with more early adopters. We welcome your enquiry: info@synaptic-labs.com