SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

Safe and Secure Real-Time (SSRT) Architecture

*statically time analysable and improves use of all alternate timing analysis approaches

* 1 to 28 cpu core

* cache-coherent architecture

* Clock-cycle perfect timing isolation WITH constant time memory address space partitioning

* Near linear scalable performance

* Large private memories

* Deterministic peripheral bandwidth

* Even static timing analysis on the SSRT architecture will be very high performance, because the hardware is very predictable and fast

The SSRT architecture will deliver the world's first HIGH PERFORMANCE industrially relevant, time-analysable, shared memory, multi-bus master platform WITH CLOCK-CYCLE PERFECT TIMING ISOLATION and with CONSTANT TIME MEMORY ADDRESS SPACE PARTITIONING.

The Safe and Secure Real-time (SSRT) computer architecture is the answer to published top priority Government and industry needs for a predictable multi-core architecture that offers high performance, is area efficient, real-time capable, supports multi-core and many-core computers, on which both general purpose and real-time software can run concurrently with higher performance and safety.

The current practices in real-time systems are summarized well by Benny Akesson, Mitra Nasri, Geoffrel Nelissen, Sebastian Altmeyer and Robert I. Davis in their 2021 paper “ Real-Time Systems, A comprehensive survey of industry practice in realtime systems”. SLL’s SSRT architecture is specifically designed for timing predictability, thereby making the work easier for designers in the widest range of real-time applications, irrespective of whichever timing analysis techniques are employed. On the SSRT architecture, even with many cores and many bus-master peripherals, real-time software will be as easy to write, verify, certify and maintain as it is today on single-bus master computer architectures.

To achieve this, several years of foundational cross-domain research and industrial needs analysis has led to the SSRT universal computer architecture designs for multiple industries that are commercially viable, even in the soft logic of COTS FPGA chips – even the tiny devices with only 2k or more 4-to-1 programmable logic elements.

The designs systematically eliminate or control all timing and performance problems at the source, in the hardware, with no changes needed to application software and no changes or minimal porting for O/S, while ensuring that all shared memory and message passing paradigms and all real-time operating system types (ARINC-653, AUTOSAR 2.0, …) can be supported.

The SSRT project is processor agnostic. For rapid market penetration, the project is currently targeting unmodified Nios II soft cores and will be deployable in ASIC and most Altera FPGAs. The SSRT project will increase the performance and capabilities of the unmodified Nios II/e and Nios II/f soft cores, while reducing the circuit area required to achieve key capabilities. Particular attention is drawn to the Intel ARRIA 10 range for safety critical applications (including DO-254 DAL A avionics), and the Max 10 range with in-built FLASH targeted to automotive and industrial control.

SSRT is specifically designed for real-time and mixed criticality applications. It is designed to provide better performance at any given price/performance point. It will help all real-time system designers, no matter which timing analysis techniques they employ, to create safer and more secure software with high performance.

By saying SSRT is designed to support a golden standard of fast static time analysability, we also mean SSRT will support and improve the results when using any other timing analysis approaches. The SSRT architecture is designed to make it easier to get good results.

The SSRT project offers a portfolio of innovative technologies. Patents are awarded. Collectively, these innovations work together for complete solutions. Also, individual innovations can be employed to achieve specific capabilities. The SSRT portfolio includes the following 3 foundational technologies. Key capabilities of those technologies are already successfully prototyped in VDHL, for use with Intel FPGA devices.

SSRT Foundational Technology 1.

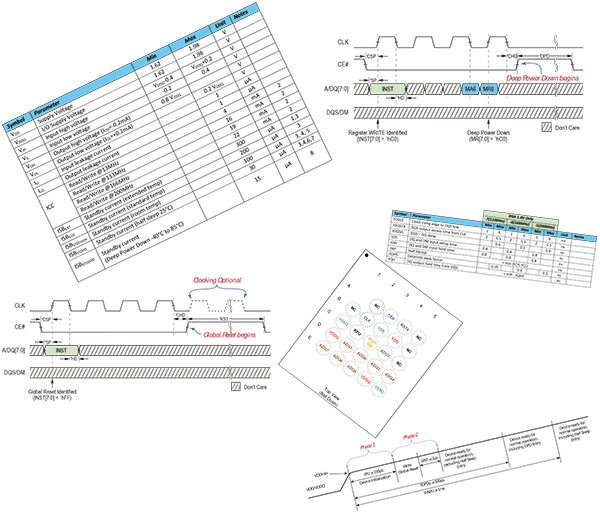

A FAST tiny STATICALLY TIME ANALYSABLE memory management unit (PATENTS AWARDED)

- Is designed to simultaneously improve both the average case execution time (ACET) and worst case execution time (WCET) of all tasks accessing SRAM, SDRAM, and FLASH.

- Designed to support all safety and security certified real-time operating systems (RTOS).

- Requires significantly less circuit area than conventional paged MMU architectures.

- ‘One-level’ MMU achieves 1 clock-cycle constant time virtual to physical address translation.

- In tiny circuit area it supports ‘two-level’ MMU constructions, to enable hardware virtualisation in multi-bus-master systems. This permits lower-assurance RTOS to be used concurrently with higher-assurance RTOS.

You can read more about this innovative memory management solution here.

SSRT Foundational Technology 2.

A FAST statically time analysable cache subsystem:

- Is designed to improve the best-effort performance of software tasks accessing a private SDRAM channel when compared to conventional commercial off the shelf (COTS) ACET optimised caches used in FPGA.

- Is designed to simultaneously improve the upper-bound WCET measurements of tasks accessing a private SDRAM channel by up to approximately 5 times when using AbsInt’s aiT tool.

- Is designed to achieve significantly faster real-time software acceleration than all probabilistic time analysable schemes that employ random cache-line eviction techniques.

- One (small) body of code performs multiple caching functions for most common memory types, including serial and parallel flash acceleration at no extra circuit area cost.

- Is designed to support very high-bandwidth, very low-latency, statically time analysable cache coherency between cores.

SSRT Foundational Technology 3.

Patents awarded and pending

A FAST statically time analysable shared memory subsystem with cache-coherent interconnect:

- Is designed to provide statically time analysable high-bandwidth messaging between cores.

- Is designed to guarantee wire-speed bandwidth with zero timing jitter for all real-time bus-master peripherals in a multi-core system, with zero reduction in software performance. As a result, the interconnect achieves high concurrency without resource starvation. This provides support for high precision capture and storage of sensor data, and guarantees that actuator data is available to peripheral/s on time, every time.

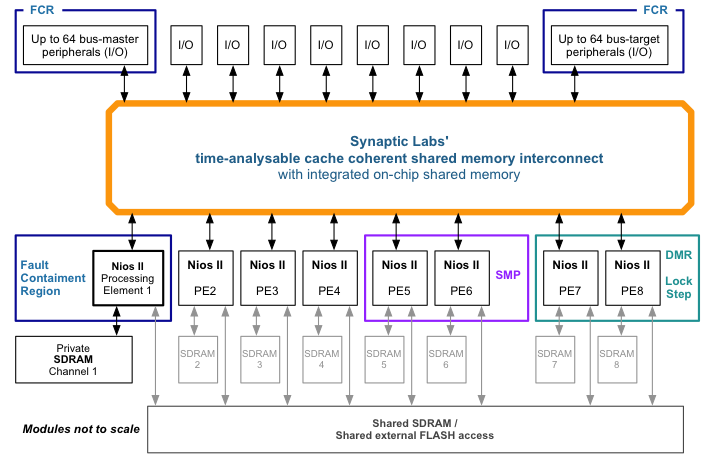

- The interconnect employs robust time and address space partitioning between every core and every bus-master. Specifically, failure containment is maintained between every {bus master, bus target} tuple. If one {core, peripheral} pair fails, that fault is isolated from other cores.

- Soft fault controls are available, including optional support for error correcting controls.

- Is designed for resource constrained environments. See diagrams below for illustrations of possible applications in single, dual, multi- and many core safety critical and mixed criticality applications.

NOT JUST FOR HIGH PERFORMANCE STATIC TIME ANALYSIS

In addition to supporting and significantly improving upper bound WCET results in static time analysis, the SSRT portfolio of technologies is also designed to support upper-bound WCET analysis using measurements based techniques. It is also designed to reduce the level of risk present when using in-house measurements based techniques (as is common in certain segments of the cyber-physical industry).

When combined together, the SSRT portfolio of technologies are explicitly designed to enable the creation of statically time-analyzable, multi-industry, computer architectures, even in low-cost FPGA’s. They will increase the performance of the single core and achieve near linear scaling of real-time shared memory software performance from 1 to 28 cores. Wire-speed bandwidth for 1 to 64 real-time bus master peripherals is guaranteed, and on-chip memory can scale from 16 to 1024-bit width data paths shared between all bus-masters. The mixed criticality multi-core architectures employ a tiny two-level memory management unit (MMU) with constant time physical to virtual address translation, and a new real-time interconnect that can sustain two (up to) 1024-bit wide cache-coherent memory transfer requests per clock cycle. Hardware controls support inter and intra-core mixed criticality. Covert timing channel attacks can also be eliminated between all bus-masters. This one architecture can be scaled for use in resource constrained Intel and other FPGA vendor’s FPGA devices with as little as 2k (4-to-1) logic elements, through to computationally intensive many-core systems in high performance FPGA devices or ASIC.

Various foundational capabilities of the Safe and Secure Real-time (SSRT) project have been successfully prototyped.

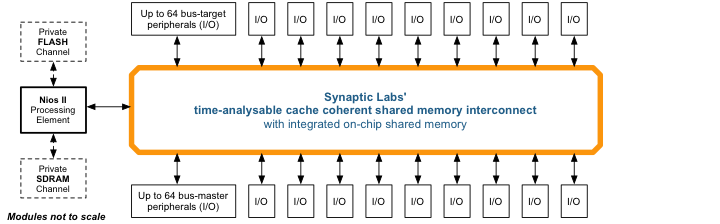

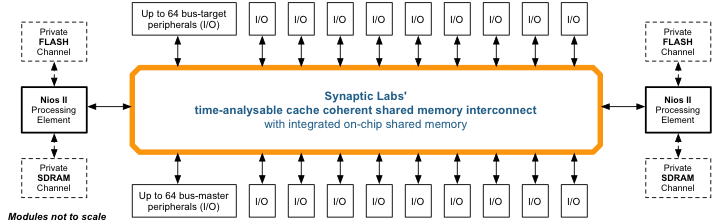

Illustrating various architectural configurations

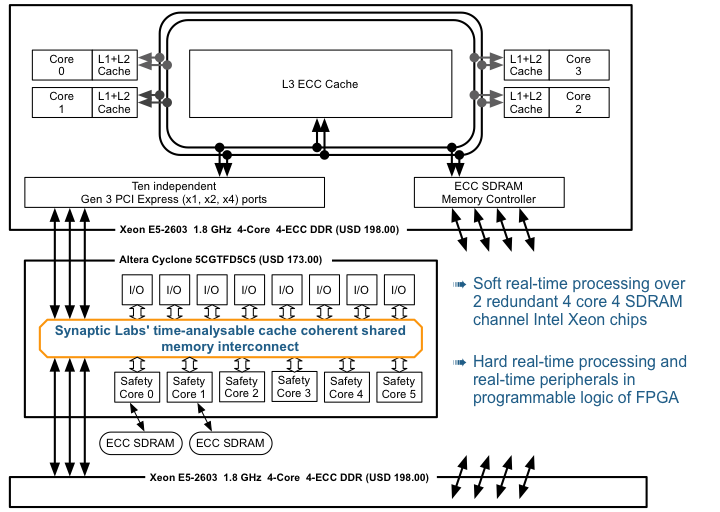

Synaptic Labs’ cache-coherent interconnect can be employed in a wide range of configurations, from real-time single-core multi-bus master deployments to many-core configurations. The interconnect can be used with soft-cores (in FPGA), and/or with hard-cores (in FPGA), and/or with soft and hard macro cores, and/or with hard cores located in external COTS ASIC chips. Other architectural configurations are also possible.

Interconnect in single-core configuration

Interconnect in dual-core configuration

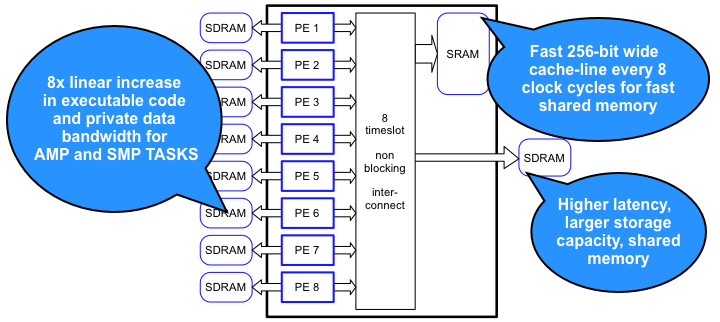

Interconnect in eight-core configuration in FPGA

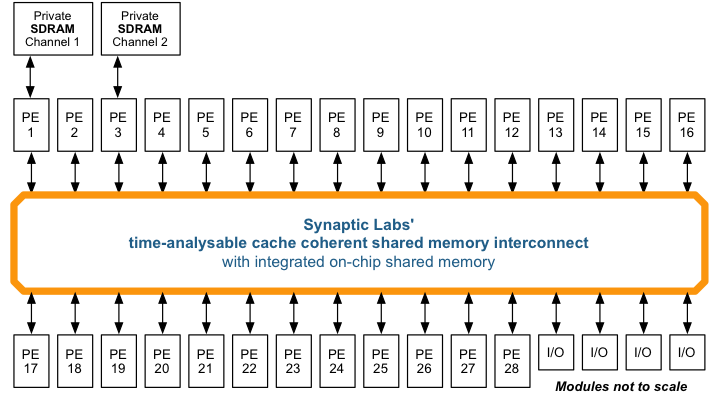

Interconnect in twenty eight core configuration in FPGA

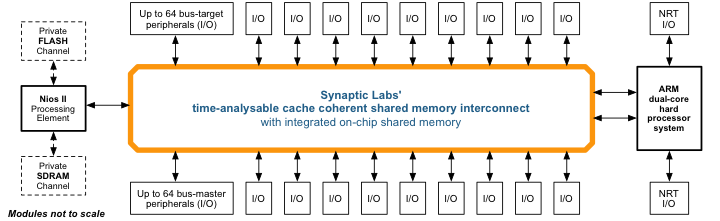

Interconnect in one soft-core and two ARM hard core configuration in FPGA

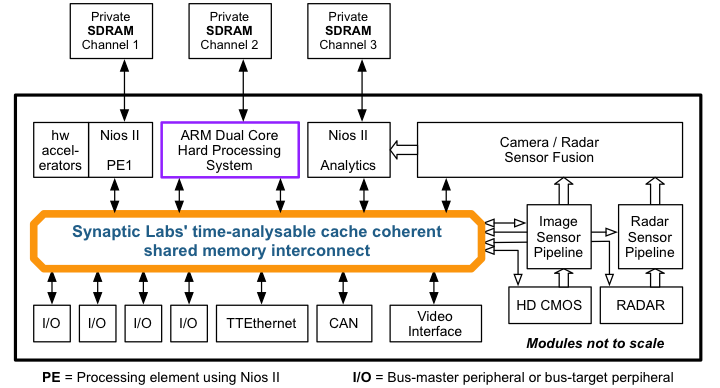

Interconnect in two soft-core and two ARM hard core with sensor fusion modules in FPGA

Interconnect with 5 soft cores in FPGA with two external Intel Xeon processors

Contact SLL for any other information about SSRT: info@synaptic-labs.com