SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

SLL is Winbond’s partner

Micron Technology, Inc

SLL collaborates closely with Micron

SLL collaborates closely with Macronix

SLL is Trenz Electronic’s partner

SLL is GigaDevice’s partner

SLL is JSC’s partner

SLL is an Infineon Associated Partner

xSPI MBMC overview

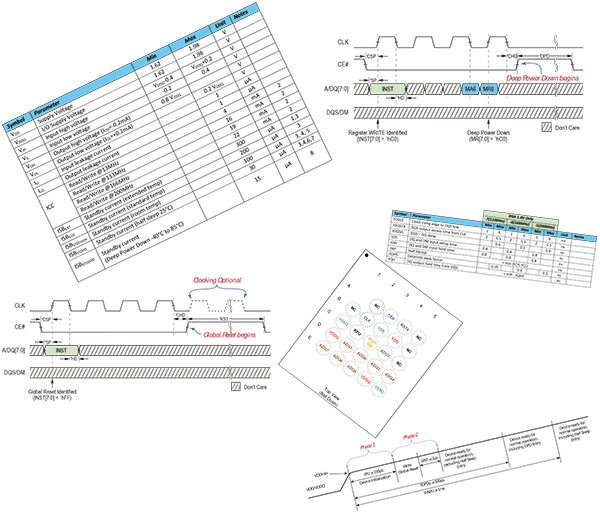

SLL’s unified xSPI Multiple Bus Memory Controller IP supports the widest range of JEDEC xSPI and xSPI-like NOR Flash and PSRAM memories (JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0, 2.0 and 3.0, OctaBus and Xccela Bus) that are available now from many memory vendors.

JEDEC xSPI and xSPI-like memories offer good performance with lower hardware and power costs. Memory device variants offer up to 512 Mbit PSRAM, up to 2 Gigabit NOR Flash, up to 250 MHz DDR clock speeds, with x4, x8 and x16 data path widths, and a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints. Some PRSAM devices are now also available with internal ECC.

SLL’s official partners include many of the leading global memory vendors. SLL works closely with our partners to ensure SLL’s memory controllers are physically qualified with their memory device variants, significantly reducing your project’s risks. SLL’s xSPI MBMC is internally verified by SLL with an extensive end-to-end test bench that achieves near 100% code coverage.

SLL’s small xSPI MBMC IP enables you to easily evaluate, select and adopt the benefits of the latest xSPI-style memories in your projects and products.

SLL provides world class pre-sales and post-sales technical support for all the major memory vendors and FPGA vendors, helping you navigate the rapidly evolving market, on the platform of your choice.

Get to market faster, with lower power consumption, lower pin count, lower cost, and far lower project risk by using SLL’s memory controller in your project/s.

xSPI MBMC v3 support for Microchip (Microsemi) FPGA

SLL’s Multiple Bus Memory Controller (xSPI-MBMC) has already been ported, and physically qualified with, Microchip PolarFire FPGA

SLL is Microchip (Microsemi)’s chosen memory controller vendor to support 1.8V HyperBus, OctaRAM and Xccela PSRAM devices at up to the full 200 MHz on Microchip PolarFire.

xSPI MBMC IP is complementary to PolarFire’s DDRx solutions:

- Supports GUI configuration in Libero

- Up to 19x less FPGA Logic Elements (LE) than x16 DDR3L controller

- Up to 5x less FPGA I/O pins than x16 DDR3L

- Up to 4x less FPGA I/O pins than x8 DDR3L

- RISC-V software performance on 8-bit PSRAM @ 200 MHz is highly competitive with 16-bit DDR3 @ 333 MHz

Contact us at info@synaptic-labs.com to enroll for the Beta under our Early Access Program.

Trials of SLL IP for FPGA and SoC FPGA

To request a Trial of SLL’s IP for FPGA and SoC FPGA, please visit here.

SLL memory device support on FPGA and SoC FPGA

SLL’s memory controller portfolio supports a very broad range of memory devices from many memory vendors.

xSPI MBMC IP currently supports, or will very soon support:

- AP Memory® Xccela™ PSRAM, OctaRAM™ and QSPI DDR PSRAM

- Everspin® SPI Industrial STT-MRAM Persistent Memory (EM064LX)

- Gigadevice® NOR Flash (GD25X, GD25LX)

- Infineon® HyperRAM™ 2.0 with HyperBus™ Interface and HyperRAM™ 2.0 with Octal Interface

- Infineon® Semper™ Flash with HyperBus™ Interface and Semper™ Flash with Octal Interface

- Infineon® (Cypress®) HyperFlash™ 1.0

- Integrated Silicon Solution Inc.® (ISSI) HyperRAM™ 1.0 (Revision D dies or higher only), HyperRAM 1.0™ with inbuilt ECC and HyperFlash™ 1.0

- ISSI® x8 Octal RAM and Octal RAM with inbuilt ECC

- ISSI® x8 Octal Flash (NOR Flash)

- ISSI® x8 Octal MCP

- Jeju Semiconductor Corp® (JSC) OctaRAM™

- Macronix® OctaBus™ / OctaFlash™ (NOR Flash)

- Micron® Xccela™ Flash (NOR Flash)

- Winbond® HyperRAM™ 1.0 and HyperRAM™ 2.0

- Winbond® OctalNAND for use with Linux (W35N01JW, W35N02JW, W35N04JW)

Contact SLL for more information: info@synaptic-labs.com