SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

Fast chip to chip communications over Octa, Octal and xSPI Profile 2.0 PSRAM protocols

SLL is Trenz Electronic’s partner

SLL is Winbond’s partner

SLL is a Microchip (Microsemi) CompanionCore Partner

SLL is a Microchip (Microsemi) CompanionCore Partner

SLL’s IP supports Xilinx FPGA devices

SLL is GigaDevice’s partner

SLL is JSC’s partner

SLL collaborates closely with Macronix

SLL is an Infineon Associated Partner

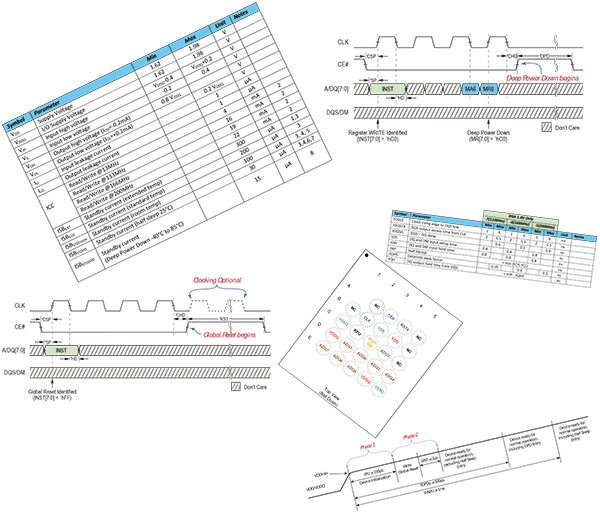

This SLL IP enables high-bandwidth, low latency, bidirectional chip to chip communications over Octa, Octal and xSPI memory protocols.

For Tightly coupled BIDIRECTIONAL communications between:

⚡ Your chosen ASIC microcontroller unit (MCU) ↔︎ your chosen FPGA

⚡ Your chosen ASIC microprocessor unit (MPU) ↔︎ your chosen FPGA

⚡ Your chosen FPGA’s: FPGA ↔︎ FPGA

- IP core has been tested with OCTOSPI peripheral in STM32L4+ and STM32L5 Series MCUs

- Is compatible with a broad range of MCU memory controllers, and:

- SLL’s xSPI Multiple Bus Memory Controller (xSPI-MBMC) IP v3.x operating in:

- HyperRAM(TM) 1.0 mode

- HyperRAM(TM) 2.0 mode

- JEDEC xSPI Profile 2.0 PSRAM mode

- Send an email to info@synaptic-labs.com with questions about compatibility with your preferred microcontroller unit (MCU).

- SLL’s xSPI Multiple Bus Memory Controller (xSPI-MBMC) IP v3.x operating in:

- Supports up to 200 MHz DDR clock speed

- Relies on a strict subset of the PSRAM commands of JEDEC xSPI – Profile 2.0.

- Supports xSPI burst read / write operations for high effective memory bandwidth.

- Supports “xSPI Profile 2.0 Standard Command Modifier Format” and “xSPI Profile 2.0 Extended Command Modifier Format”.

- Multiplexes two communications channels over the xSPI channel to enable bidirectional communications.

- Each communications channel implements a bin-based flow control algorithm for high performance.

- Can support most FPGA vendors device families including but not limited to:

- Intel FPGA’s and SoC’s including Cyclone 10 LP, Max10, etc

- Xilinx Series-7 families including UltraScale and UltraScale+

- Supports Standard cell ASIC

- This IP core is internally verified by SLL with an extensive end-to-end test bench that achieves near 100% code coverage.

- Send an email to info@synaptic-labs.com with requests for support on other targets. Also for information on evaluation hardware with free trial IP.

Contact SLL for information on many development board options for all these memory vendors xSPI memory devices: info@synaptic-labs.com