SLL's embedded software innovation has been recognised by our customers and partners. Major FPGA, memory, and development board makers now officially partner with SLL. This ensures SLL IP is validated on a wide range of physical devices. SLL customers are located in most geographical regions, and include Fortune Global 500's, government agencies, and SME's from USA and Canada to China.

About Synaptic Laboratories Ltd (SLL)

- Creates COTS soft IP products for use in hardware

- Licenses cores globally for use in FPGA and ASIC

- Creates IP’s on customer request

- Invents large scale innovations (patents awarded)

- Provides specialist domain services

- Delivers excellent customer service

- Supports Partners FAE and customers in many regions

LATEST NEWS

Get more from your FPGA and

SoC FPGA configuration flash!

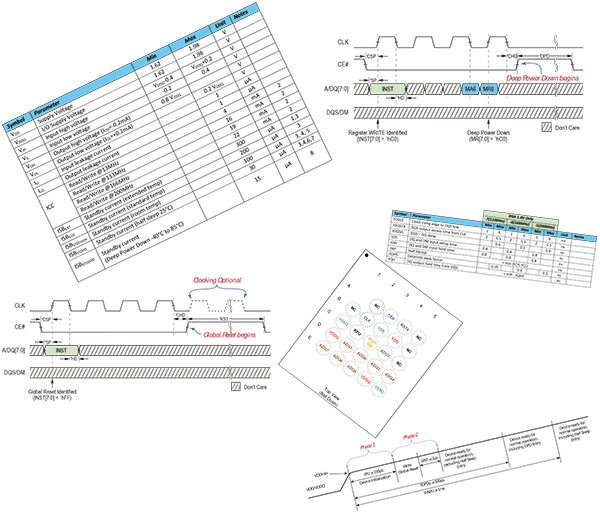

The newest addition to SLL’s IP portfolio allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, 200 MHz DDR x8 NOR Flash. Your design will continue to power-on in legacy SPI mode, to configure the FPGA with normal SPI performance.

The difference: SLL IP instantiated in the FPGA fabric enables access to the x8 configuration NOR Flash device in high throughput 200 MHz DDR 8D-8D-8D mode, for far superior run-time performance after boot.

So, selecting a 200 MHz DDR xSPI configuration flash gives your design so much more. It can reduce your BoM through potentially less memories in your design, less board area, and increased run-time system performance with lower pin-count. Also suitable for use with very low pin count multi-chip packages which combine PSRAM and NOR Flash die in the one BGA24 package. SLL’s solution natively supports Intel Quartus Programmer for maximum ease of use. Also supports exciting STT-MRAM for non-volatile memory with PSRAM like read/write performance.

Supported FPGA device families include:

- Intel Cyclone 10LP, Cyclone IV, Cyclone V, Cyclone 10 GX, Arria V, Arria 10, Stratix V, Stratix 10, Agilex 10

- Ask about Xilinx 7-Series support.

Read more here.

Products

SHOWCASE SLL PRODUCT:

xSPI Multiple Bus Memory Controller (xSPI MBMC)

-

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported INTEL FPGA's and SoC's: All families.

SLL is an Intel Internet of Things (IoT) and Design Solutions Partner (Gold)

Intel chose SLL memory controller IP to bundle and distribute globally with the Intel Cyclone 10LP Eval Kit.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol. -

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported MICROCHIP / MICROSEMI FPGA's and SoC's: POLARFIRE (others upon request)

SLL is the Microchip CompanionCore partner for xSPI memory controller IP.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol. -

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported XILINX FPGA's and SoC's: All Xilinx Series-7 families, including UltraScale and UltraScale + (others upon request)

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol. -

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Other supported FPGA's and SoC's: Many can be supported - upon request. For example: Efinix, Lattice, etc.

Contact SLL for all your support needs on info@synaptic-labs.com.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol. -

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC) FOR ASIC

SLL IS ALREADY WORKING WITH GLOBAL LEADERS TO PORT XSPI-MBMC IP TO ASIC IN THEIR PROJECTS.

SLL’S IP IS BASED ON EXTENSIVE COMMERCIAL USE IN FPGA’S AND PHYSICAL VALIDATION IN A WIDE RANGE OF FPGA AND SOC FAMILIES.

FOR MORE INFORMATION ABOUT XSPI-MBMC IP FOR YOUR ASIC PROJECT PLEASE CONTACT here.

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported INTEL FPGA’s and SoC’s: All families.

SLL is an Intel Internet of Things (IoT) and Design Solutions Partner (Gold)

Intel chose SLL memory controller IP to bundle and distribute globally with the Intel Cyclone 10LP Eval Kit.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.

ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol.

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported MICROCHIP / MICROSEMI FPGA’s and SoC’s: POLARFIRE (others upon request)

SLL is the Microchip CompanionCore partner for xSPI memory controller IP.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.

ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol.

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Supported XILINX FPGA’s and SoC’s: All Xilinx Series-7 families, including UltraScale and UltraScale + (others upon request)

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.

ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol.

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC)

Other supported FPGA’s and SoC’s: Many can be supported – upon request. For example: Efinix, Lattice, etc.

Contact SLL for all your support needs on info@synaptic-labs.com.

Supports protocols: JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus, Octal Bus, Xccela Bus. These xSPI-like memories offer good performance with lower hardware and power costs.

Supports memory vendors: ~ nine. This gives you multiple sources of long term supply, with a wide range of device sizes and capabilities for maximum design flexibility and choice.

Memory vendors partner with SLL for physical validation of xSPI MBMC on their memories and mutual customer support.

Memory options include: up to 250 MHz DDR, with x4, x8 and x16 data paths; a wide range of package options including 4mm x 4mm BGA49 and tiny WLCSP footprints; some PRSAM devices with internal ECC; exciting xSPI STT-MRAM; and very low I/O pin count multi chip packages (PSRAM with Flash).

SLL is the subject domain expert and successfully supports Fortune Global 500’s, government agencies and contractors, and SME’s to successfully adopt these exciting xSPI-like memories.

ABOUT xSPI MBMC IP:

This single IP supports the wide range of xSPI-style NOR Flash and PSRAM memories that are available now from many memory vendors. xSPI MBMC and xSPI memories have very low resource costs. xSPI MBMC IP enables you to easily evaluate and switch between the supported protocols to select the best supported memory devices for your projects. Additionally, xSPI MBMC IP also allows you to replace your design’s slow SPI or QSPI configuration flash with a fast, low pin count, up to 250 MHz DDR x8 NOR Flash.

READ MORE about xSPI MBMC here.

Additionally, xSPI MBMC IP also supports SLL’s Chip-to-Chip IP to deliver high bandwidth, low latency communications between {ASIC MCU <-> FPGA}, and {FPGA <-> FPGA} over xSPI protocol.

MULTIPLE BUS MEMORY CONTROLLER FOR xSPI TYPE MEMORIES (xSPI MBMC) FOR ASIC

SLL IS ALREADY WORKING WITH GLOBAL LEADERS TO PORT XSPI-MBMC IP TO ASIC IN THEIR PROJECTS.

SLL’S IP IS BASED ON EXTENSIVE COMMERCIAL USE IN FPGA’S AND PHYSICAL VALIDATION IN A WIDE RANGE OF FPGA AND SOC FAMILIES.

FOR MORE INFORMATION ABOUT XSPI-MBMC IP FOR YOUR ASIC PROJECT PLEASE CONTACT here.

SHOWCASE SLL PRODUCT:

Fast chip to chip communications over octa / octal / xSPI

-

Chip to chip communications over octa / octal / xSPI

High-bandwidth, low latency, bidirectional communications

for [ASIC microcontroller unit (MCU) <-> FPGA],

and [ASIC microprocessor unit (MPU) <-> FPGA],

and [FPGA <-> FPGA].For example, SLL’s chip to chip peripheral is compatible with STMicroelectronics OCTOSPI memory controller, and tested with STM32L4+ and STM32L5 devices.

Use-case: ASIC MCU or MPU <-> FPGA

Use this IP to enable high bandwidth, low latency, tightly coupled communications between your chosen ASIC MCU/MPU and your chosen FPGA. This will maximise the price and performance advantages of both the MCU/MPU and FPGA devices. The memory controller on the ASIC MCU or MPU is configured to use either Octal PSRAM, HyperRAM or xSPI Profile 2.0 PSRAM protocol.The software running on the ASIC MCU or MPU takes advantage of fast software execution. Software has access to Ethernet and other lowcost peripherals inside the MCU/MPU in the usual way. Software running in the ASIC MCU or MPU sends and receives data to and from the targeted FPGA, over the memory controller in the ASIC MCU or MPU.

SLL’s chip to chip peripheral is easily instantiated in the FPGA fabric of your chosen FPGA (Intel, Microchip, Xilinx, …). The IP receives and responds to those memory transfer requests, to enable fast bidirectional communications between the chips.

Use-case: FPGA <-> FPGA

Instantiate SLL’s xSPI Multiple Bus Memory Controller (xSPI MBMC) IP v3 in the host FPGA, and instantiate the chip to chip peripheral on the target FPGA. This enables high bandwidth, low latency, tightly coupled communications between those two FPGA devices. -

Chip to chip communications over octa / octal / xSPI

High-bandwidth, low latency, bidirectional communications

for [ASIC microcontroller unit (MCU) <-> FPGA],

and [ASIC microprocessor unit (MPU) <-> FPGA],

and [FPGA <-> FPGA].For example, SLL’s chip to chip peripheral is compatible with STMicroelectronics OCTOSPI memory controller, and tested with STM32L4+ and STM32L5 devices.

ASK SLL ABOUT SUPPORT FOR YOUR PROJECT’S MCU OR MPU on info@synaptic-labs.com.

Chip to chip communications over octa / octal / xSPI

High-bandwidth, low latency, bidirectional communications

for [ASIC microcontroller unit (MCU) <-> FPGA],

and [ASIC microprocessor unit (MPU) <-> FPGA],

and [FPGA <-> FPGA].

For example, SLL’s chip to chip peripheral is compatible with STMicroelectronics OCTOSPI memory controller, and tested with STM32L4+ and STM32L5 devices.

Use-case: ASIC MCU or MPU <-> FPGA

Use this IP to enable high bandwidth, low latency, tightly coupled communications between your chosen ASIC MCU/MPU and your chosen FPGA. This will maximise the price and performance advantages of both the MCU/MPU and FPGA devices. The memory controller on the ASIC MCU or MPU is configured to use either Octal PSRAM, HyperRAM or xSPI Profile 2.0 PSRAM protocol.

The software running on the ASIC MCU or MPU takes advantage of fast software execution. Software has access to Ethernet and other lowcost peripherals inside the MCU/MPU in the usual way. Software running in the ASIC MCU or MPU sends and receives data to and from the targeted FPGA, over the memory controller in the ASIC MCU or MPU.

SLL’s chip to chip peripheral is easily instantiated in the FPGA fabric of your chosen FPGA (Intel, Microchip, Xilinx, …). The IP receives and responds to those memory transfer requests, to enable fast bidirectional communications between the chips.

Use-case: FPGA <-> FPGA

Instantiate SLL’s xSPI Multiple Bus Memory Controller (xSPI MBMC) IP v3 in the host FPGA, and instantiate the chip to chip peripheral on the target FPGA. This enables high bandwidth, low latency, tightly coupled communications between those two FPGA devices.

Chip to chip communications over octa / octal / xSPI

High-bandwidth, low latency, bidirectional communications

for [ASIC microcontroller unit (MCU) <-> FPGA],

and [ASIC microprocessor unit (MPU) <-> FPGA],

and [FPGA <-> FPGA].

For example, SLL’s chip to chip peripheral is compatible with STMicroelectronics OCTOSPI memory controller, and tested with STM32L4+ and STM32L5 devices.

ASK SLL ABOUT SUPPORT FOR YOUR PROJECT’S MCU OR MPU on info@synaptic-labs.com.

SHOWCASE SLL PRODUCT:

The HyperBus 1.0 Memory Controller (HBMC) v3.1.x

-

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

SUPPORTED INTEL FPGA’s AND SOC’s: Most families.

SLL is an INTEL IIoT and Design Solutions Partner (Gold).

Intel chose SLL memory controller IP to bundle and distribute globally with the Intel Cyclone 10LP Eval Kit.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors. -

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Supported MICROCHIP / MICROSEMI FPGA's and SoC's: POLARFIRE (others upon request)

SLL is the Microchip CompanionCore partner for xSPI memory controller IP.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors. -

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Supported XILINX FPGA's and SoC's: Xilinx Series-7 families. For all others including UltraScale and UltraScale+ use xSPI-MBMC IP.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors. -

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Contact SLL for all your support needs on info@synaptic-labs.com.

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

SUPPORTED INTEL FPGA’s AND SOC’s: Most families.

SLL is an INTEL IIoT and Design Solutions Partner (Gold).

Intel chose SLL memory controller IP to bundle and distribute globally with the Intel Cyclone 10LP Eval Kit.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors.

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Supported MICROCHIP / MICROSEMI FPGA’s and SoC’s: POLARFIRE (others upon request)

SLL is the Microchip CompanionCore partner for xSPI memory controller IP.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors.

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Supported XILINX FPGA’s and SoC’s: Xilinx Series-7 families. For all others including UltraScale and UltraScale+ use xSPI-MBMC IP.

This small IP supports all the HyperFlash Generation 1.0 devices sold by from multiple memory vendors. This includes all HyperRAM, HyperFlash and HyperMCP (MultiChip Package) Generation 1.0 devices. Read more about HBMC here.

SLL also supports customers transitioning to the faster and lower power HyperBus Generation 2.0 devices. This requires SLL’s xSPI MBMC IP. For the best HyperBus and xSPI memory controller you should always select SLL’s xSPI MBMC IP. This is because the xSPI MBMC IP :

– Supports all the HyperBus 1.0 devices; and

– Supports all the faster, and even lower power, HyperBus 2.0 devices; and

– Supports the OctaBus, Xccela Bus and similar devices; and

– It is very easy to swap between all these xSPI and xSPI-like protocols using xSPI MBMC IP; and

– xSPI MBMC IP supports more FPGA device families from the major FPGA vendors; and

– xSPI MBMC IP gives you maximum design flexibility and choice of suppliers for xSPI-type memories and FPGA families supported; and

– You can choose from the wider range of devices offered by our many memory partners and supported FPGA vendors.

HyperBus 1.0 Memory Controller (HBMC) V3.1.x

Contact SLL for all your support needs on info@synaptic-labs.com.

SLL products are highly innovative and generally easy to use

SHOWCASE SLL PRODUCT:

SLL’s Tiny Cache T003 for Intel FPGAs.

Potentially huge software performance acceleration with extremely low resource costs e.g. for Nios II/e and /f designs. This product is a tiny, high performance, set-associative write-through cache for use with on-chip and off-chip flash. Read more here.

Inventions

SHOWCASE SLL INVENTION:

Breakthrough embedded Memory Management (MMU) / Memory Protection (MPU) Solutions.

Patents awarded (USA, South Korea, … ) and pending in many countries. This invention offers significant technical advances over existing MMU’s and MPU’s in the majority of 32-bit and 64-bit embedded designs.

This tiny footprint solution delivers exceptional real-time memory management capabilities for processors and peripherals in embedded systems.

Tiny footprint allows for MMU/MPU capabilities even in very resource constrained designs. Options include combining the most important features and capabilities of a memory protection unit (MPU) and a memory management unit (MMU) in ONE tiny module. Read more here.

SHOWCASE SLL INVENTION:

Breakthrough multi- and many-core Safe and Secure RealTime Architecture (SSRT). Multiple patents awarded. SSRT will:

- support all realtime operating systems

- processor agnostic

- statically time analysable and improves use of all alternate timing analysis approaches

- simplifies writing realtime software

- higher performance

- and more.

Read more about SSRT here.

Patents Awarded from USA to Asia!

SLL customers use our soft IP's in a very wide range of applications

Customers

SLL supplies IP to, and supports our customers in, many countries. This includes customers in the USA and Canada, in EU member states including Germany, Italy, France and others, in China and Japan, in Switzerland and in countries in other regions. SLL has an excellent track record of supporting our customers to project success. This includes Fortune Global 500’s, specialist companies that are global leaders in their fields, national research institutions, government agencies, and small to medium sized enterprises.

SLL customers also include FPGA and ASIC design houses, that are making products and systems for important customers and also for governments, including the USA.

CUSTOMERS APPLICATIONS

Customers use SLL IP’s:

- in a very wide range of applications

- on a wide range of FPGA device families from several FPGA device vendors.

Some SLL IP is now being ported to ASIC.

Read more about our customers and how they use SLL’s IP’s here.

SLL Memory, FPGA and Board Partners

Memory Partners:

SLL’s official partners include many of the leading global memory vendors. SLL works closely with our partners to ensure SLL’s memory controllers are physically qualified with their memory device families.

FPGA Partners:

SLL has official partnerships with Intel and Microchip (Microsemi). SLL IP supports a very broad range of Intel FPGA device families, and MCHP’s PolarFire family. SLL IP also supports a very broad range of Xilinx FPGA device families. SLL’s IP can be ported to support others FPGA vendors, including Efinix and Lattice.

Board Partners:

SLL partners also include board makers that bundle SLL IP with their COTS development boards and System-on-Modules (SoM). This includes Intel, Trenz Electronic and Aries Embedded. Due to the close collaboration between SLL and our board partners, memory partners and FPGA partners, it is now possible for you to access very low cost COTS evaluation and development boards. This means customers can quickly and very cheaply evaluate many of the new JEDEC xSPI, HyperBus, OctaBus and Xccela Bus memories supported by SLL’s memory controller IP’s on a range of FPGA device families.

SLL Reference Designs:

SLL reference designs have been downloaded thousands of times. We provide reference designs with our Free Trial and Production IP’s, so customers can start easily and quickly.

Read more about our partners here.

SLL's domain expertise and ecosystem of partnerships delivers comprehensive customer support

Services

SHOWCASE SLL SERVICE:

JEDEC xSPI and xSPI-like memory domain expertise.

SLL arguably offers the most comprehensive domain expertise support services for the wide range of JEDEC xSPI Profile 1.0 and 2.0, HyperBus 1.0 and 2.0, OctaBus and Xccela Bus memories from our many memory vendor partners.

SLL have years of expertise and experience supporting very large and small projects through to success on a wide range of FPGA device families from multiple FPGA vendors. Our skills and our extensive circle of partnerships is available to support you, to ensure your projects success at lowest cost, in lowest time, and with lowest risk.

SHOWCASE SLL SERVICE:

Intel FPGA Quartus Platform Designer resource shrink and performance optimisation.

SLL designers can significantly reduce the circuit area and improve static timing of complex Nios II/f and Avalon based Quartus Platform Designer (QSYS) projects. Fit more in your target FPGA device, or aim to select a smaller, cheaper, lower power FPGA device. Optionally add xSPI and xSPI-like memories to reduce pin count and power costs. Read more here.

Contact us for more information info@synaptic-labs.com.

Free Trials

Free Trials and Reference Designs:

SLL provides free trials with reference designs for several of our IP’s. SLL reference designs have been downloaded thousands of times. Contact us to request your free trial here!

SLL as Expert Intermediary:

SLL’s extensive circle of partners means customers can rely on SLL as a one stop shop for a wide range of domain expertise for our IP’s. As the official partner of many of the manufacturers, SLL receives fast support from our partners on behalf of our customers whenever needed.

Join our email mailing list:

If you would like to receive the latest domain expert news on xSPI and xSPI-like memories and SLL’s memory controllers, then please register for our free Newsletter. We promise we will not spam you or share your details.